Đề thi, bài tập trắc nghiệm Kiến trúc máy tính online - Đề #5

Vui lòng cài đặt đề thi trước khi làm bài

Xét sơ đồ phân cấp hệ thống nhớ, phát biểu nào sau đây là sai:

Xét sơ đồ phân cấp hệ thống nhớ, phát biểu nào sau đây là đúng:

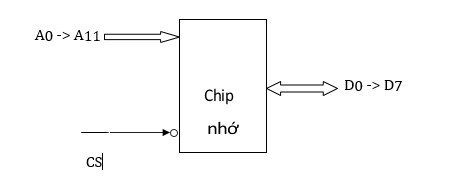

Cho chip nhớ như hình vẽ, đây là ký hiệu của:

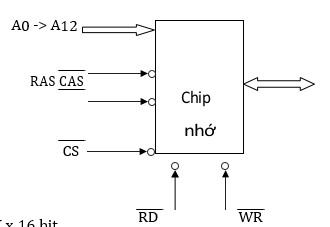

Cho chip nhớ như hình vẽ, đây là ký hiệu của:

Đối với bộ nhớ chính (BNC) máy tính, phát biểu nào sau đây là sai:

Đối với bộ nhớ chính (BNC) máy tính, phát biểu nào sau đây là đúng:

Đối với bộ nhớ cache, phát biểu nào sau đây là đúng:

Đối với bộ nhớ cache, phát biểu nào sau đây là đúng:

Khi CPU truy nhập cache, có hai khả năng sau:

Cache hoạt động nhờ vào nguyên lý:

Trong sự trao đổi giữa cache và bộ nhớ chính, phát biểu nào sau đây là sai:

Xét bộ nhớ cache, mỗi line được gắn thêm Tag là để:

Xét bộ nhớ cache, có các kỹ thuật ánh xạ địa chỉ sau đây:

Trong kỹ thuật ánh xạ liên kết hoàn toàn, các trường địa chỉ là:

Trong kỹ thuật ánh xạ trực tiếp, các trường địa chỉ là:

Trong kỹ thuật ánh xạ liên kết tập hợp, các trường địa chỉ là:

Cho máy tính có dung lượng bộ nhớ chính: 128MB, cache: 64KB, line: 8 byte, độ dài ngăn nhớ: 1 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 256MB, cache: 128KB, line: 16 byte, độ dài ngăn nhớ: 2 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 512MB, cache: 128KB, line: 64 byte, độ dài ngăn nhớ: 4 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 256MB, cache: 64KB, line: 16 byte, độ dài ngăn nhớ: 4 byte. Trong trường hợp kỹ thuật ánh xạ liên kết hoàn toàn, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 256MB, cache: 128KB, line: 32 byte, độ dài ngăn nhớ: 4 byte. Trong trường hợp kỹ thuật ánh xạ liên kết hoàn toàn, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 128MB, cache: 64KB, line: 16 byte, độ dài ngăn nhớ: 1 byte, set: 4 line. Trong trường hợp kỹ thuật ánh xạ liên kết tập hợp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 512MB, cache: 128KB, line: 32 byte, độ dài ngăn nhớ: 2 byte, set: 4 line. Trong trường hợp kỹ thuật ánh xạ liên kết tập hợp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Cho máy tính có dung lượng bộ nhớ chính: 256MB, cache: 128KB, line: 128 byte, độ dài ngăn nhớ: 4 byte, set: 8 line. Trong trường hợp kỹ thuật ánh xạ liên kết tập hợp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

Xét kỹ thuật ánh xạ trực tiếp khi truy nhập cache, thứ tự tìm block trong cache được thực hiện dựa theo các trường trong địa chỉ do CPU phát ra như sau:

Đối với bộ nhớ cache, xét kỹ thuật ánh xạ liên kết tập hợp, thứ tự tìm block trong cache được thực hiện dựa theo các giá trị trong địa chỉ do CPU phát ra như sau:

Xét các thuật toán thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng:

Đối với bộ nhớ cache, các thuật toán thay thế dữ liệu là:

Đối với các phương pháp ghi dữ liệu vào cache, phát biểu nào sau đây là sai:

Đối với các phương pháp ghi dữ liệu vào cache, phát biểu nào sau đây là đúng:

Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng:

Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là sai:

Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng:

Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là sai:

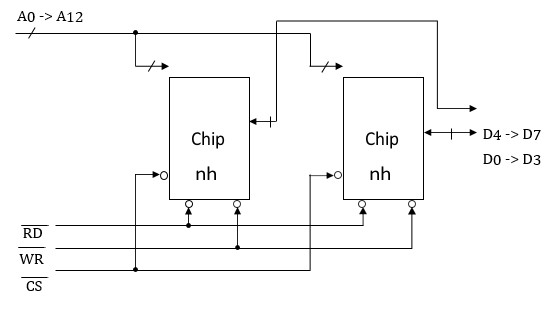

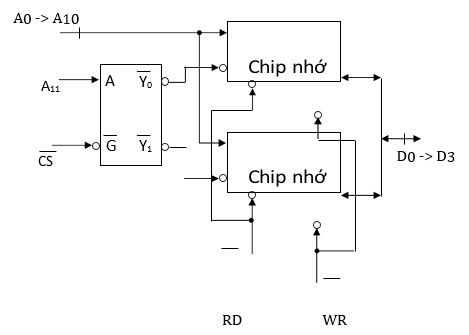

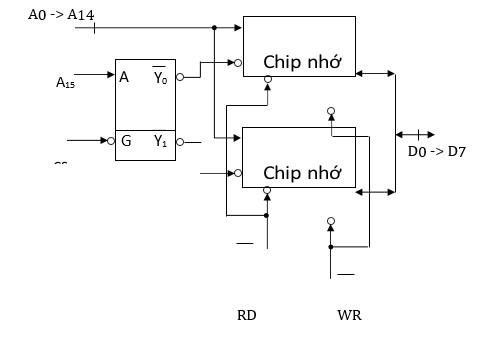

Hình vẽ dưới đây là sơ đồ kết nối của 2 IC SRAM:

:

Hình vẽ dưới đây là sơ đồ kết nối của 2 IC SRAM:

:

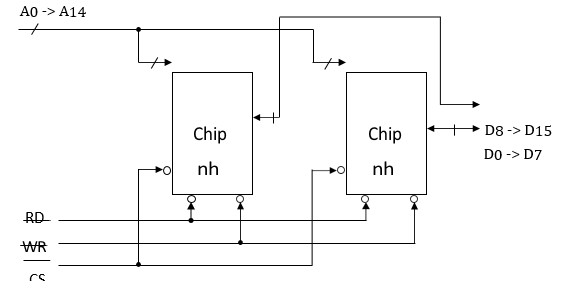

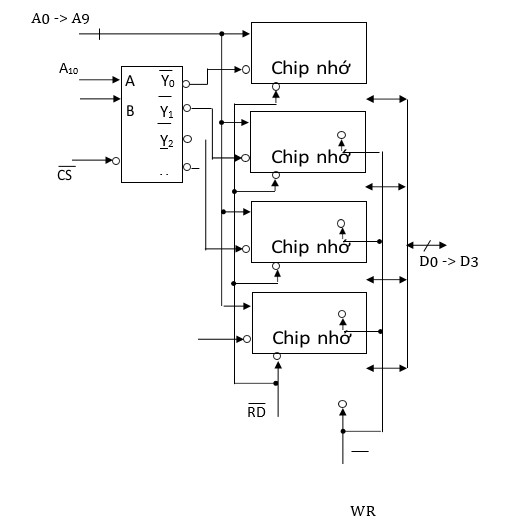

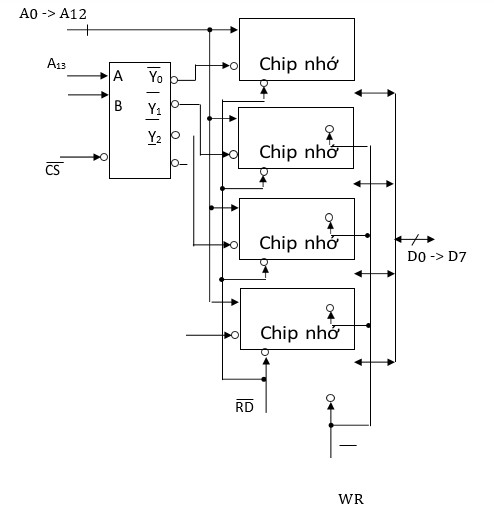

Hình vẽ dưới đây là sơ đồ kết nối của 4 IC SRAM:

:

Hình vẽ dưới đây là sơ đồ kết nối của 4 IC SRAM:

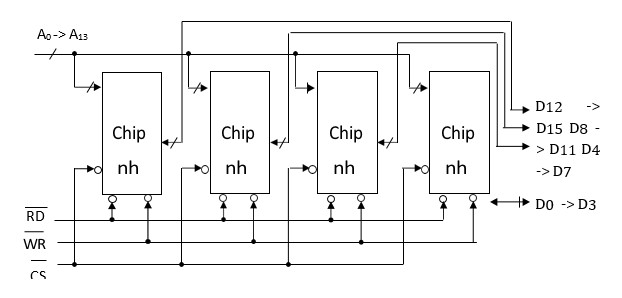

Hình vẽ dưới là sơ đồ kết nối của 2 IC SRAM:

:

Hình vẽ dưới là sơ đồ kết nối của 2 IC SRAM:

:

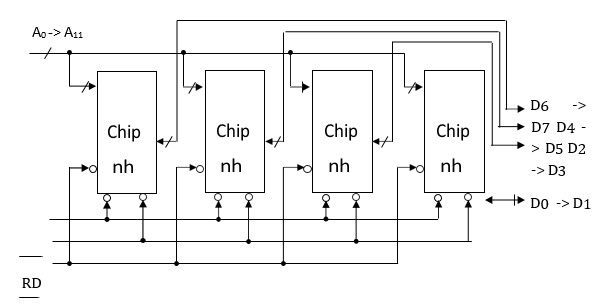

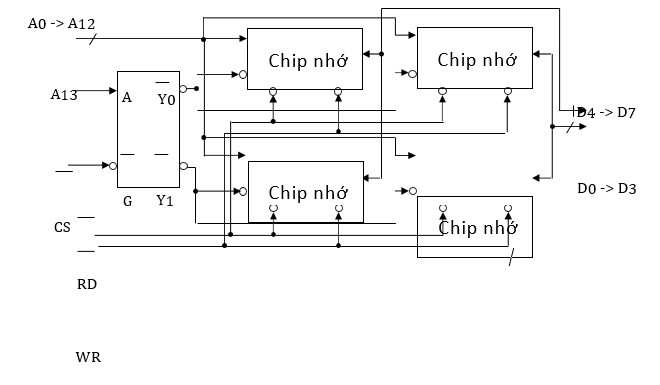

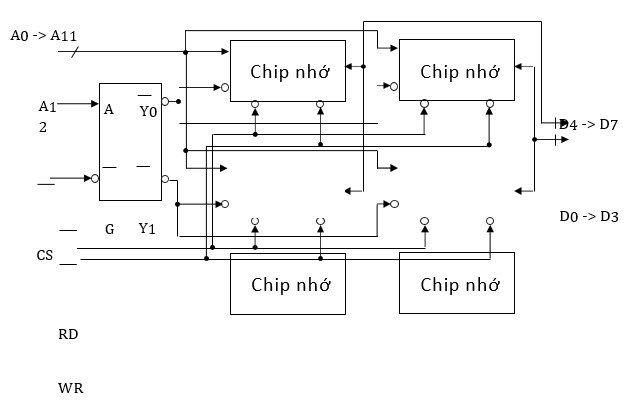

Hình vẽ dưới là sơ đồ kết nối của 4 IC SRAM:

Hình vẽ dưới là sơ đồ kết nối của 4 IC SRAM:

Hình vẽ dưới đây là sơ đồ kết nối 4 IC SRAM:

Hình vẽ dưới đây là sơ đồ kết nối 4 IC SRAM:

Với chip nhớ SRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

Với chip nhớ SRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

Với chip nhớ DRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

Với chip nhớ DRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

Đối với bộ nhớ cache, xét nguyên lý định vị về thời gian, phát biểu nào sau đây là đúng:

Đối với bộ nhớ cache, xét nguyên lý định vị về không gian, phát biểu nào sau đây là đúng: